## Ultra Efficient Dual Sources Energy Manager with Ratio/Constant Voltage Regulation, Regulated Buck Output and 5 V Charger

### Features and Benefits

#### Dual sources inputs

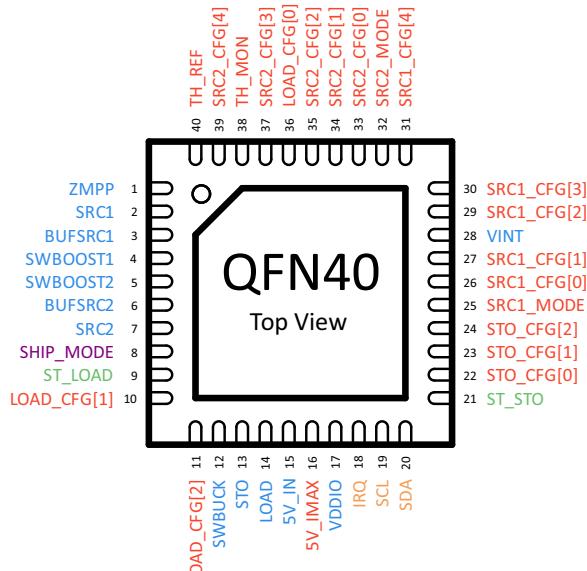

- Boost operation optimized for each source.

- Conversion efficiency above 90 % on each source.

- Harvests from 120 mV after cold start.

- Simultaneous harvesting from both sources.

- Up to 135 mA current extracted from the harvester.

#### Maximum Power Point Tracking

- Both sources configurable to constant voltage mode or to open-circuit voltage ratio mode.

- Optimal harvesting from a multiple combinations of harvesters (PV cells, RF, vibration, pulsed sources...).

#### Cold start from 275 mV / 1.5 $\mu$ W input

- Startup at ultra-low power from each harvesting source input.

#### Configurable overdischarge & overcharge protection

- Supports various types of rechargeable storage elements (LiC, Li-ion, LiPo, Li-ceramic pouch...).

#### Regulated output for application circuit

- Buck regulator conversion efficiency up to 96 %.

- Selectable output voltage between 0.6 V and 3.3 V.

- Output current up to 100 mA.

#### Thermal monitoring

- Storage element protection against over-temperature and under-temperature during charging and discharging, independently.

#### Average Power Monitoring

- Provides data to determine how much energy has been transferred to the storage from each source and from the 5 V charger, as well as the energy drained from the storage to supply the application circuit.

#### System configuration by GPIO or I<sup>2</sup>C communication

- All settings dynamically configurable through GPIO or I<sup>2</sup>C (Fast Mode Plus).

- System data available through I<sup>2</sup>C.

#### Shipping mode

- Storage element charge and discharge disabling during shipment.

#### External 5 V charging capability

- Extra charging input for 5 V power supplies.

- Configurable CC and CV modes (max. 135 mA).

- Provides a fast charging alternative when no source is available for a long time.

### Applications

|                |                   |

|----------------|-------------------|

| Smart home     | Industrial sensor |

| Smart building | Retail            |

| Edge IoT       | PC accessories    |

### Description

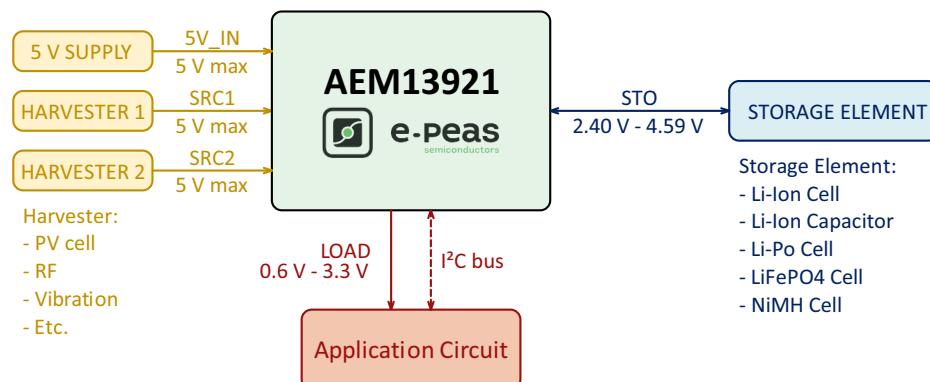

The AEM13921 is a fully integrated and compact power management circuit that extracts DC power from two harvesting sources to store energy in a rechargeable storage element and supply an application circuit. A 5 V input can also be used to charge the storage element (e.g., if it gets depleted). This compact and ultra-efficient PMIC allows for extending battery lifetime and eliminating the primary energy storage in a large range of applications.

Both sources implement Maximum Power Point Tracking (MPPT) based on open-circuit voltage ratio as well as constant source voltage regulation features, allowing for harvesting the maximum power available from each source to charge the storage element.

With its unique cold-start circuit, it can start operating with an input voltage as low as 275 mV (min. 1.5  $\mu$ W power).

The configurable protection thresholds prevent overcharging and overdischarging the storage element. No external components are required to set those thresholds. The thermal monitoring prevents charging and discharging the storage element outside a configurable temperature range.

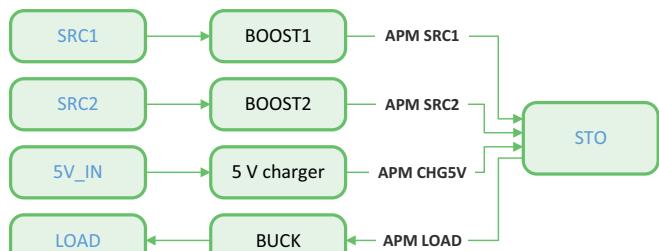

The Average Power Monitoring (APM) allows the application circuit to get an estimate of the energy harvested from each source to the battery and from the battery to the application circuit. A shipping mode is available to avoid charging and discharging the storage element during shipping or storage.

A buck regulator with selectable output voltage allows an application circuit to be supplied with high efficiency.

I<sup>2</sup>C communication allows users to control every setting of the AEM13921 from the application circuit MCU.

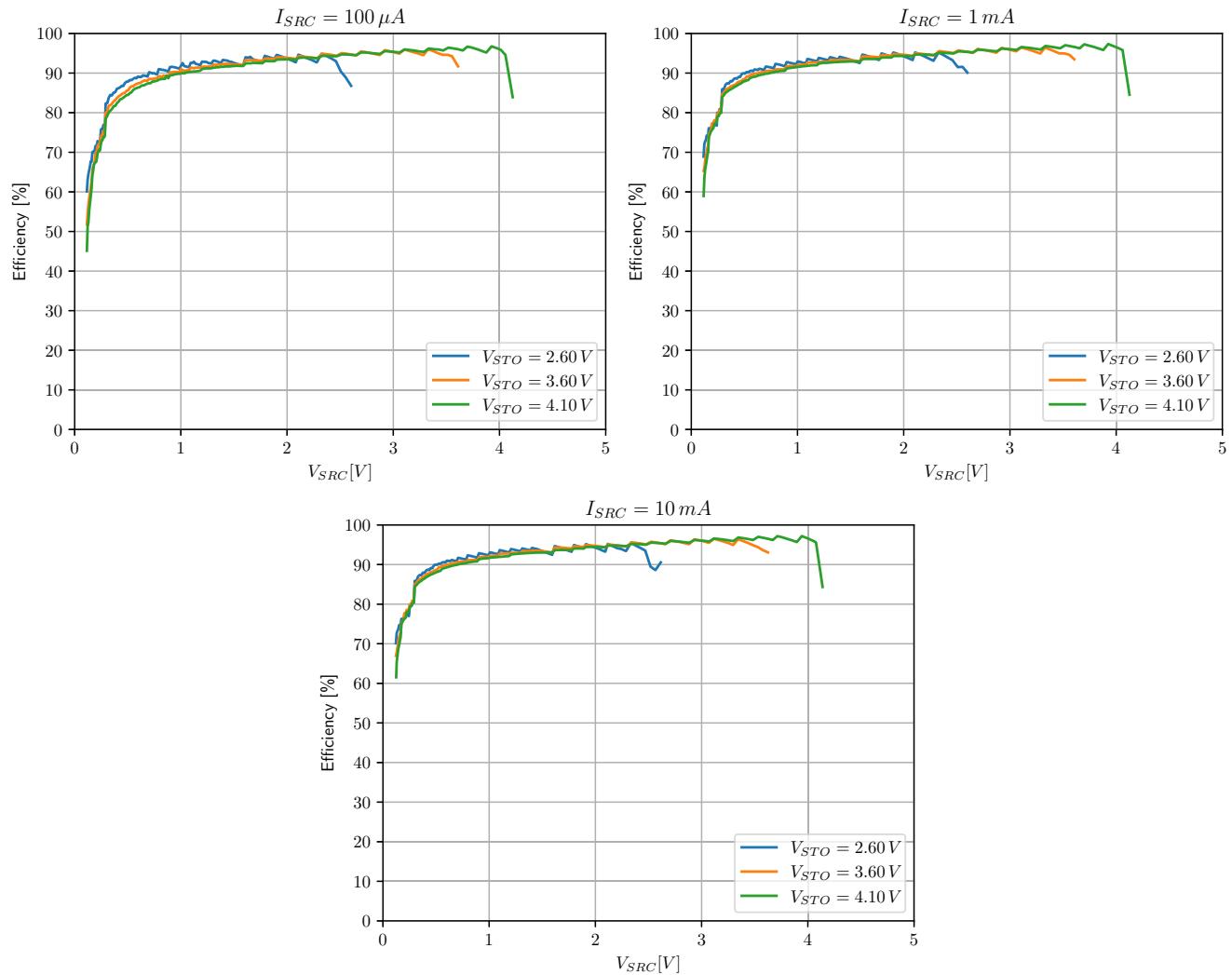

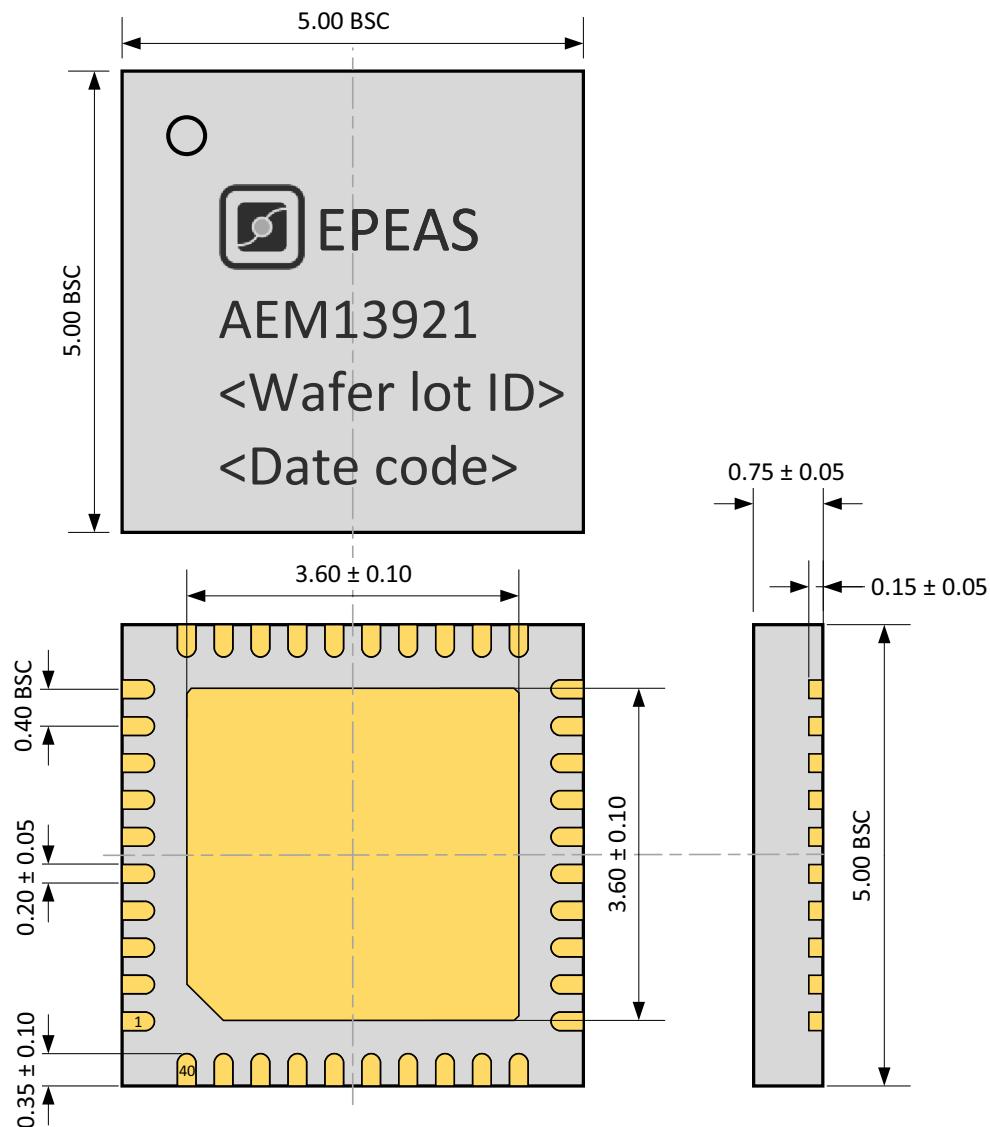

### Device Information

| Part Number     | Package    | Body size |

|-----------------|------------|-----------|

| 10AEM13921J0000 | QFN 40-pin | 5 x 5 mm  |

### Evaluation Board

| Part number    |

|----------------|

| 2AAEM13921J001 |

## Table of Contents

|                                                      |           |

|------------------------------------------------------|-----------|

| <b>1. Introduction</b>                               | <b>9</b>  |

| <b>2. Pin Configuration and Functions</b>            | <b>10</b> |

| <b>3. Specifications</b>                             | <b>13</b> |

| 3.1. Absolute Maximum Ratings .....                  | 13        |

| 3.2. ESD Ratings .....                               | 13        |

| 3.3. Thermal Resistance .....                        | 13        |

| 3.4. Electrical Characteristics at 25 °C .....       | 14        |

| 3.5. Recommended Operating Conditions .....          | 17        |

| 3.5.1. External Inductors Information .....          | 17        |

| 3.5.2. External Capacitors Information .....         | 17        |

| 3.6. Typical Characteristics .....                   | 18        |

| 3.6.1. Boost Converters Conversion Efficiency .....  | 18        |

| 3.6.2. Buck Converter Conversion Efficiency .....    | 19        |

| <b>4. Functional Block Diagram</b>                   | <b>20</b> |

| <b>5. Theory of Operation</b>                        | <b>21</b> |

| 5.1. Cold-Start Circuits .....                       | 21        |

| 5.2. Boost Converters .....                          | 21        |

| 5.2.1. Operation Principle .....                     | 21        |

| 5.2.2. Maximum Power Point Tracking .....            | 22        |

| 5.2.2.1. Open-Circuit Voltage Ratio .....            | 22        |

| 5.2.2.2. ZMPP .....                                  | 22        |

| 5.2.3. Source Constant Voltage Regulation .....      | 23        |

| 5.2.4. Automatic High-Power Mode .....               | 23        |

| 5.2.5. Using Both Boost Converters in Parallel ..... | 23        |

| 5.3. Buck Converter .....                            | 24        |

| 5.4. Thermal Monitoring .....                        | 25        |

| 5.5. Average Power Monitoring .....                  | 25        |

| 5.5.1. SRCx and LOAD APM .....                       | 25        |

| 5.5.2. 5 V Charger APM .....                         | 25        |

| 5.5.3. APM IRQ .....                                 | 26        |

| 5.5.4. APM Accumulator .....                         | 26        |

| 5.6. IRQ Pin .....                                   | 26        |

| 5.7. 5 V Charger .....                               | 26        |

| 5.7.1. CC Mode .....                                 | 26        |

| 5.7.2. CC/CV Mode .....                              | 26        |

| 5.8. Shipping Mode .....                             | 27        |

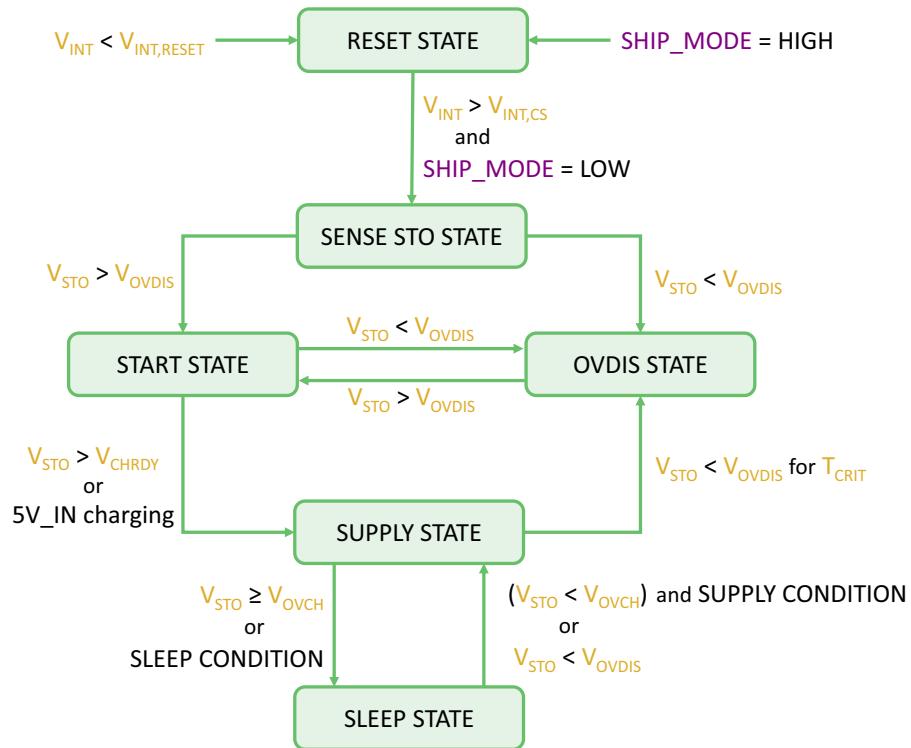

| 5.9. State Machine Description .....                 | 28        |

| 5.9.1. RESET STATE .....                             | 28        |

| 5.9.2. SENSE STO STATE .....                         | 28        |

| 5.9.3. START STATE .....                             | 29        |

| 5.9.4. SUPPLY STATE .....                            | 29        |

| 5.9.5. OVDIS STATE .....                             | 29        |

| 5.9.6. SLEEP STATE .....                             | 29        |

| <b>6. System Configuration</b>                       | <b>31</b> |

|                                                                                      |           |

|--------------------------------------------------------------------------------------|-----------|

| 6.1. Configuration Pins and I <sup>2</sup> C .....                                   | 31        |

| 6.1.1. Configuration Pins .....                                                      | 31        |

| 6.1.2. Configuration by I <sup>2</sup> C .....                                       | 31        |

| 6.2. Source Constant Voltage Regulation .....                                        | 32        |

| 6.3. Maximum Power Point Tracking .....                                              | 33        |

| 6.4. Storage Element Thresholds .....                                                | 34        |

| 6.5. Boost Converter Timings .....                                                   | 36        |

| 6.6. Buck Converter .....                                                            | 36        |

| 6.6.1. Load Voltage .....                                                            | 36        |

| 6.6.2. Buck Converter Timings .....                                                  | 36        |

| 6.7. Thermal Monitoring .....                                                        | 36        |

| 6.8. 5 V Charger .....                                                               | 37        |

| 6.9. Shipping Mode .....                                                             | 37        |

| <b>7. I<sup>2</sup>C Serial Interface Protocol</b>                                   | <b>38</b> |

| <b>8. Register Map</b>                                                               | <b>40</b> |

| <b>9. Registers Configuration</b>                                                    | <b>43</b> |

| 9.1. I <sup>2</sup> C Control (CTRL) .....                                           | 43        |

| 9.2. Version Register (VERSION) .....                                                | 43        |

| 9.3. Source Regulation (SRCxREGUx) .....                                             | 44        |

| 9.3.1. SRCxREGU0 .....                                                               | 45        |

| 9.3.2. SRCxREGU1 .....                                                               | 45        |

| 9.3.3. Constant Voltage Configuration .....                                          | 46        |

| 9.3.4. MPPT Configuration .....                                                      | 47        |

| 9.4. Source Low Threshold (SRCLOW) .....                                             | 48        |

| 9.5. Storage Element Threshold Voltages (VOVDIS / VCHRDY / VCHRDYBUCK / VOVCH) ..... | 49        |

| 9.5.1. Overdischarge Voltage (VOVDIS) .....                                          | 49        |

| 9.5.2. Charge Ready Voltage (VCHRDY) .....                                           | 50        |

| 9.5.3. Buck Charge Ready Voltage (VCHRDYBUCK) .....                                  | 51        |

| 9.5.4. Overcharge Voltage (VOVCH) .....                                              | 52        |

| 9.6. Boost Converters (BSTxCFG) .....                                                | 53        |

| 9.7. Buck Converter (BUCKCFG) .....                                                  | 54        |

| 9.8. 5 V Charger (CHG5V) .....                                                       | 55        |

| 9.9. STO Charge Temperature Protection (TEMPCOLDCH and TEMPHOTCH) .....              | 56        |

| 9.9.1. TEMPCOLDCH .....                                                              | 56        |

| 9.9.2. TEMPHOTCH .....                                                               | 56        |

| 9.10. STO Discharge Temperature Protection (TEMPCOLDDIS and TEMPHOTDIS) .....        | 57        |

| 9.10.1. TEMPCOLDDIS .....                                                            | 57        |

| 9.10.2. TEMPHOTDIS .....                                                             | 57        |

| 9.11. Thermal Protection Monitoring (TEMPPROTECT) .....                              | 58        |

| 9.12. Average Power Monitoring (APM) .....                                           | 59        |

| 9.13. APM Accumulator (APMACC) .....                                                 | 59        |

| 9.14. IRQ Enable (IRQENx) .....                                                      | 60        |

| 9.14.1. IRQENO .....                                                                 | 60        |

| 9.14.2. IRQEN1 .....                                                                 | 61        |

| 9.15. IRQ Flags (IRQFLGx) .....                                                      | 62        |

| 9.15.1. IRQFLG0 .....                                                                | 62        |

| 9.15.2. IRQFLG1 .....                                                                | 63        |

|                                                                 |           |

|-----------------------------------------------------------------|-----------|

| 9.16. Status (STATUSx) .....                                    | 65        |

| 9.16.1. STATUS0 .....                                           | 65        |

| 9.16.2. STATUS1 .....                                           | 66        |

| 9.17. APM Data Summary (APMxSRCx, APMxCHG5V and APMxLOAD) ..... | 67        |

| 9.17.1. APMxSRCx and APMxLOAD Summary .....                     | 67        |

| 9.17.2. APMxCHG5V Summary .....                                 | 68        |

| 9.18. SRCx APM Data (APMxSRCx) .....                            | 69        |

| 9.18.1. APM0SRCx .....                                          | 69        |

| 9.18.2. APM1SRCx .....                                          | 69        |

| 9.18.3. APM2SRCx .....                                          | 69        |

| 9.19. LOAD APM Data (APMxLOAD) .....                            | 70        |

| 9.19.1. APM0LOAD .....                                          | 70        |

| 9.19.2. APM1LOAD .....                                          | 70        |

| 9.19.3. APM2LOAD .....                                          | 70        |

| 9.20. CHG5V APM Data (APMxCHG5V) .....                          | 71        |

| 9.20.1. APM0CHG5V .....                                         | 71        |

| 9.20.2. APM1CHG5V .....                                         | 71        |

| 9.21. APM Error (APMERR) .....                                  | 72        |

| 9.22. Temperature Monitoring Data (TEMP) .....                  | 73        |

| 9.23. Storage Element Voltage Data (STO) .....                  | 73        |

| 9.24. Sources Voltage Data (SRCx) .....                         | 74        |

| 9.25. Part Number (PNx) .....                                   | 75        |

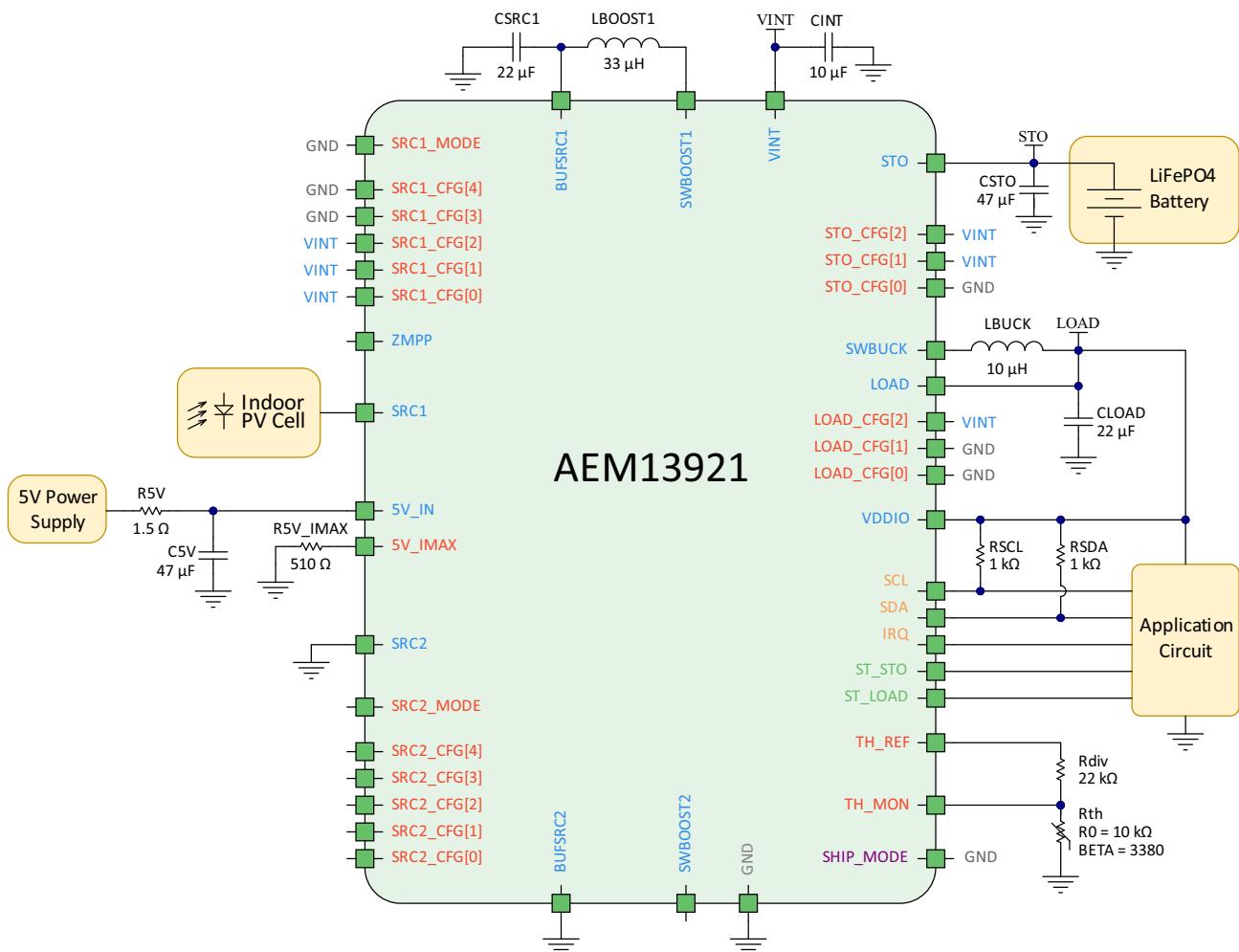

| <b>10. Typical Application Circuits</b>                         | <b>76</b> |

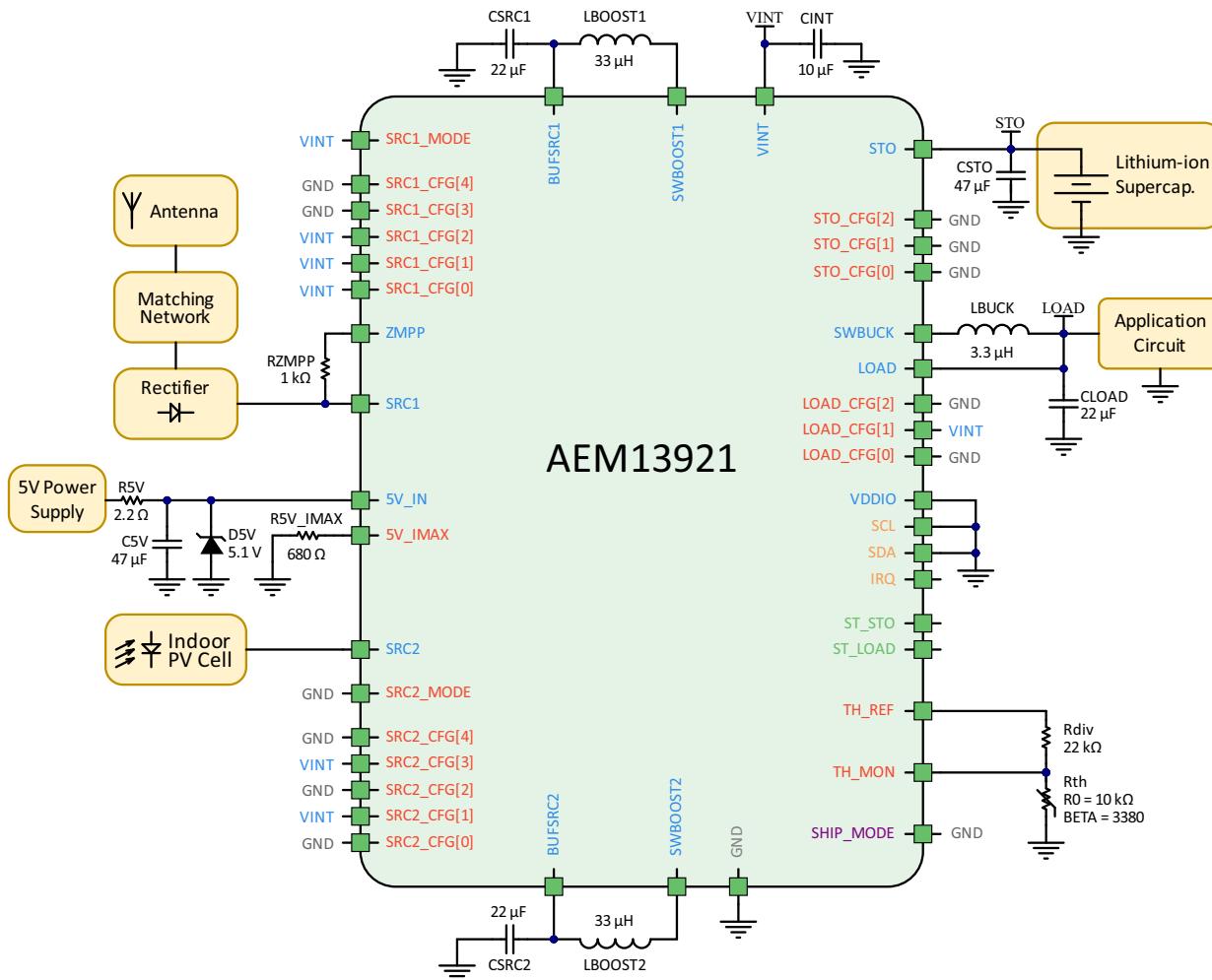

| 10.1. Example Circuit 1 .....                                   | 76        |

| 10.2. Example Circuit 2 .....                                   | 78        |

| 10.3. Example Circuit 3 .....                                   | 80        |

| <b>Table 80:</b>                                                | <b>82</b> |

| <b>11. Minimum BOM</b>                                          | <b>83</b> |

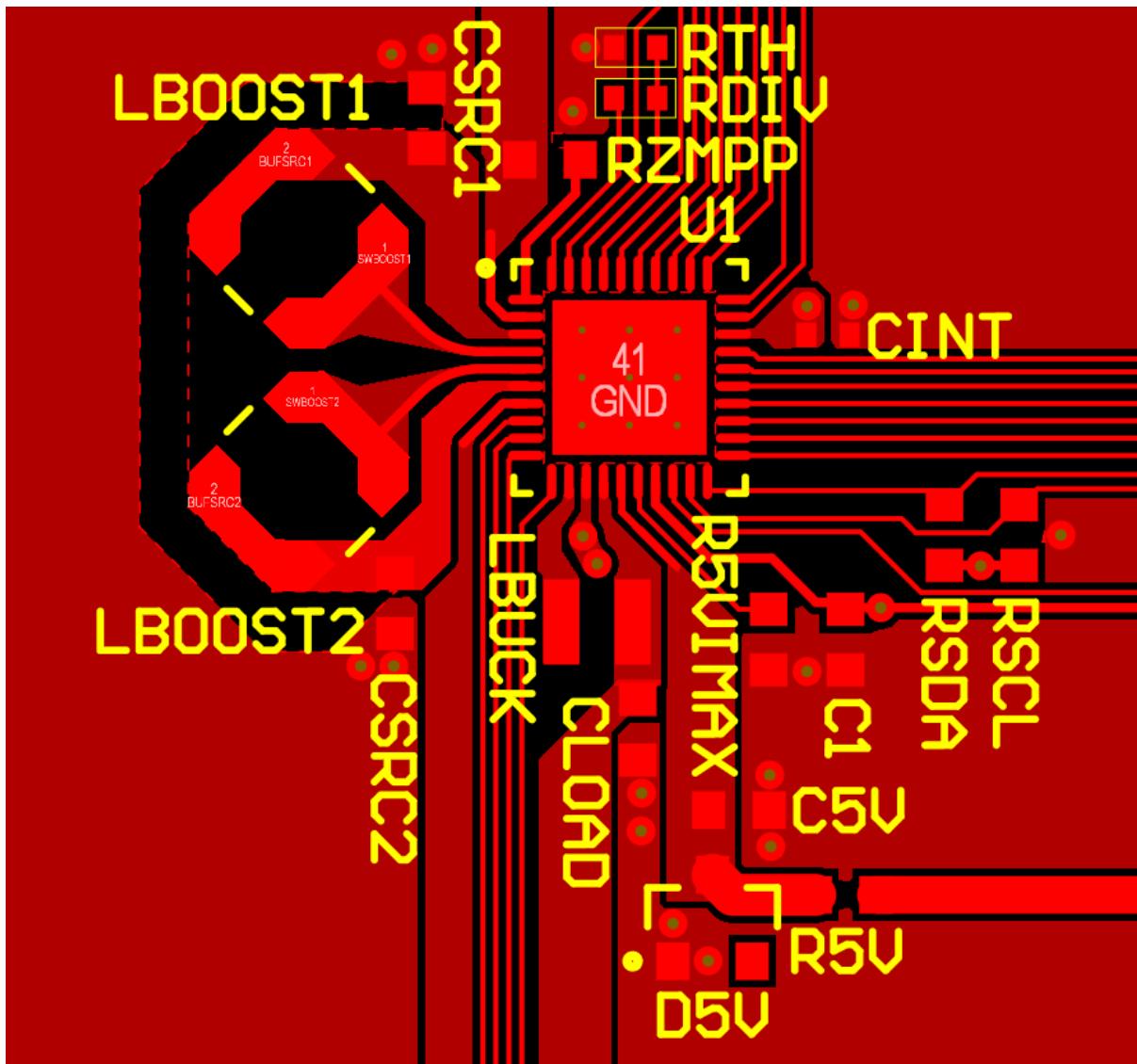

| <b>12. Layout</b>                                               | <b>84</b> |

| 12.1. Guidelines .....                                          | 84        |

| 12.2. Example .....                                             | 85        |

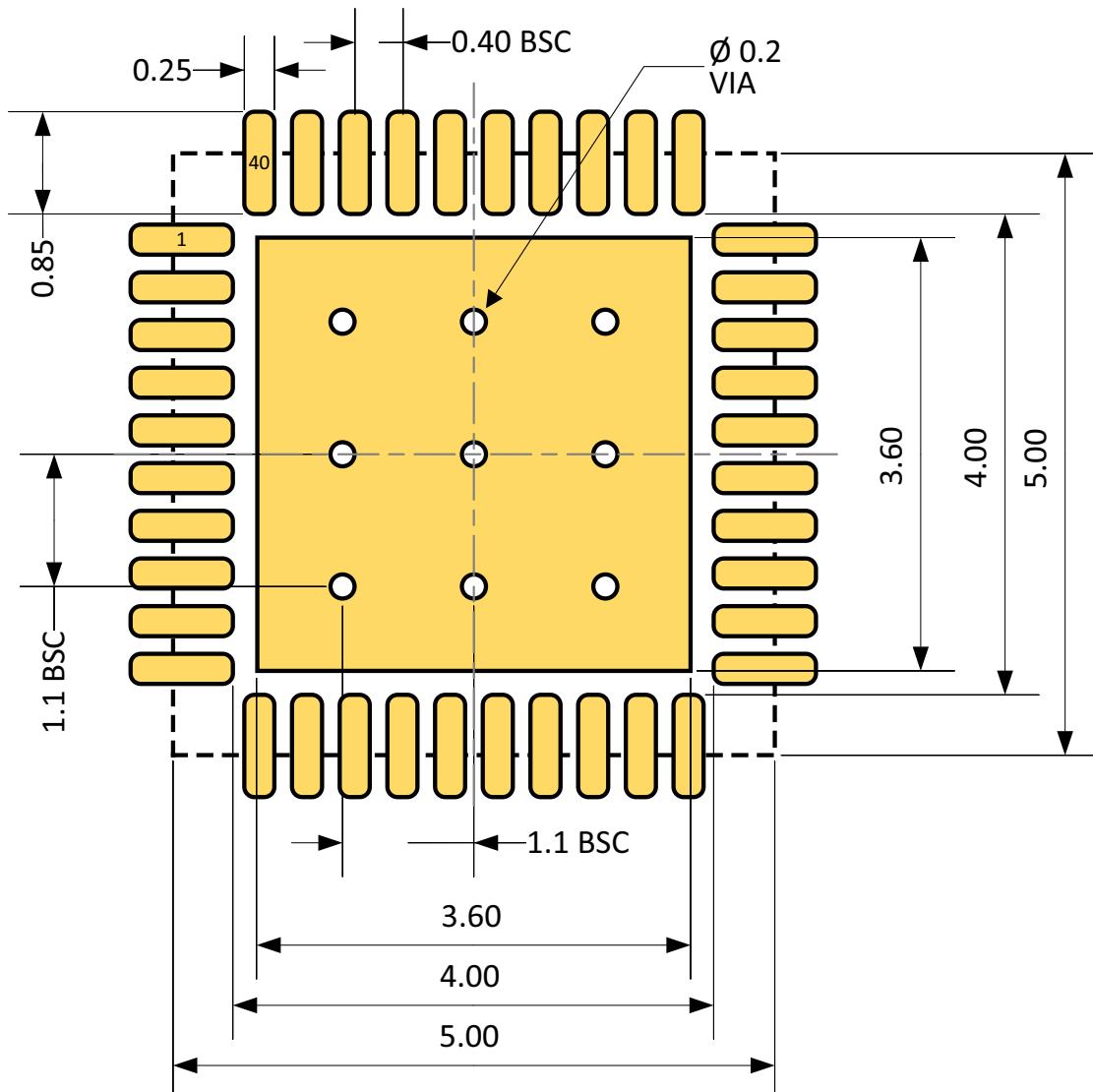

| <b>13. Package Information</b>                                  | <b>86</b> |

| 13.1. Moisture Sensitivity Level .....                          | 86        |

| 13.2. RoHS Compliance .....                                     | 86        |

| 13.3. REACH Compliance .....                                    | 86        |

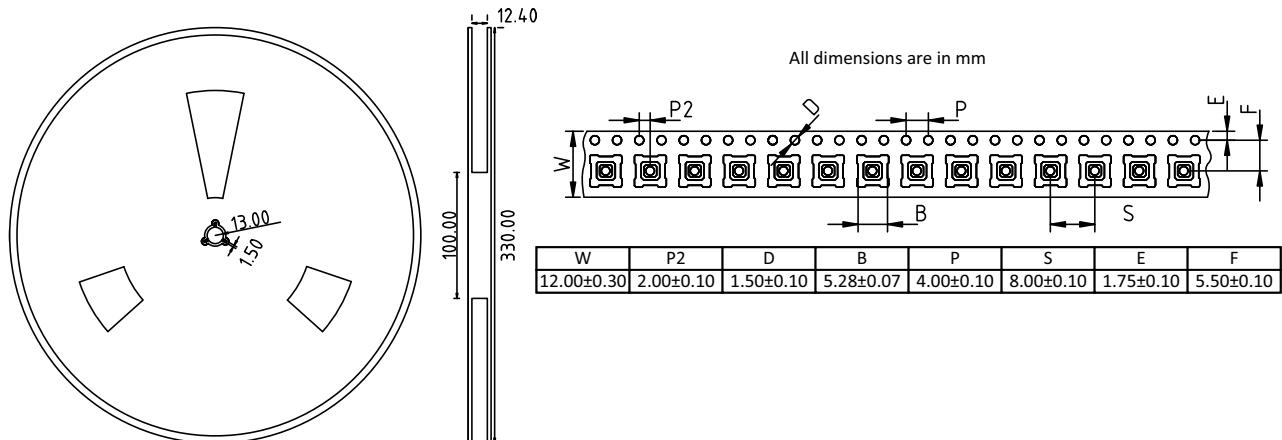

| 13.4. Tape and Reel Dimensions .....                            | 86        |

| 13.5. Package Dimensions .....                                  | 87        |

| 13.6. Board Layout .....                                        | 88        |

| <b>14. Glossary</b>                                             | <b>89</b> |

| <b>15. Revision History</b>                                     | <b>92</b> |

## List of Figures

|                                                                                                                                                   |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

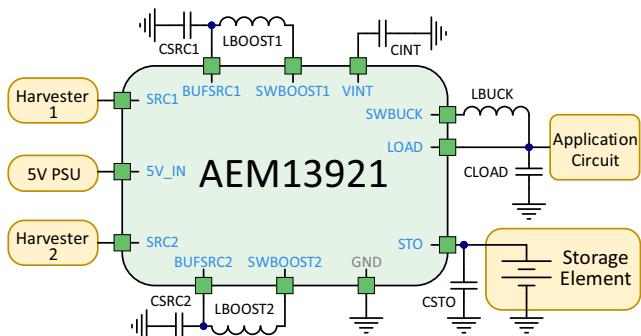

| Figure 1: Simplified schematic view .....                                                                                                         | 9  |

| Figure 2: Pinout diagram .....                                                                                                                    | 10 |

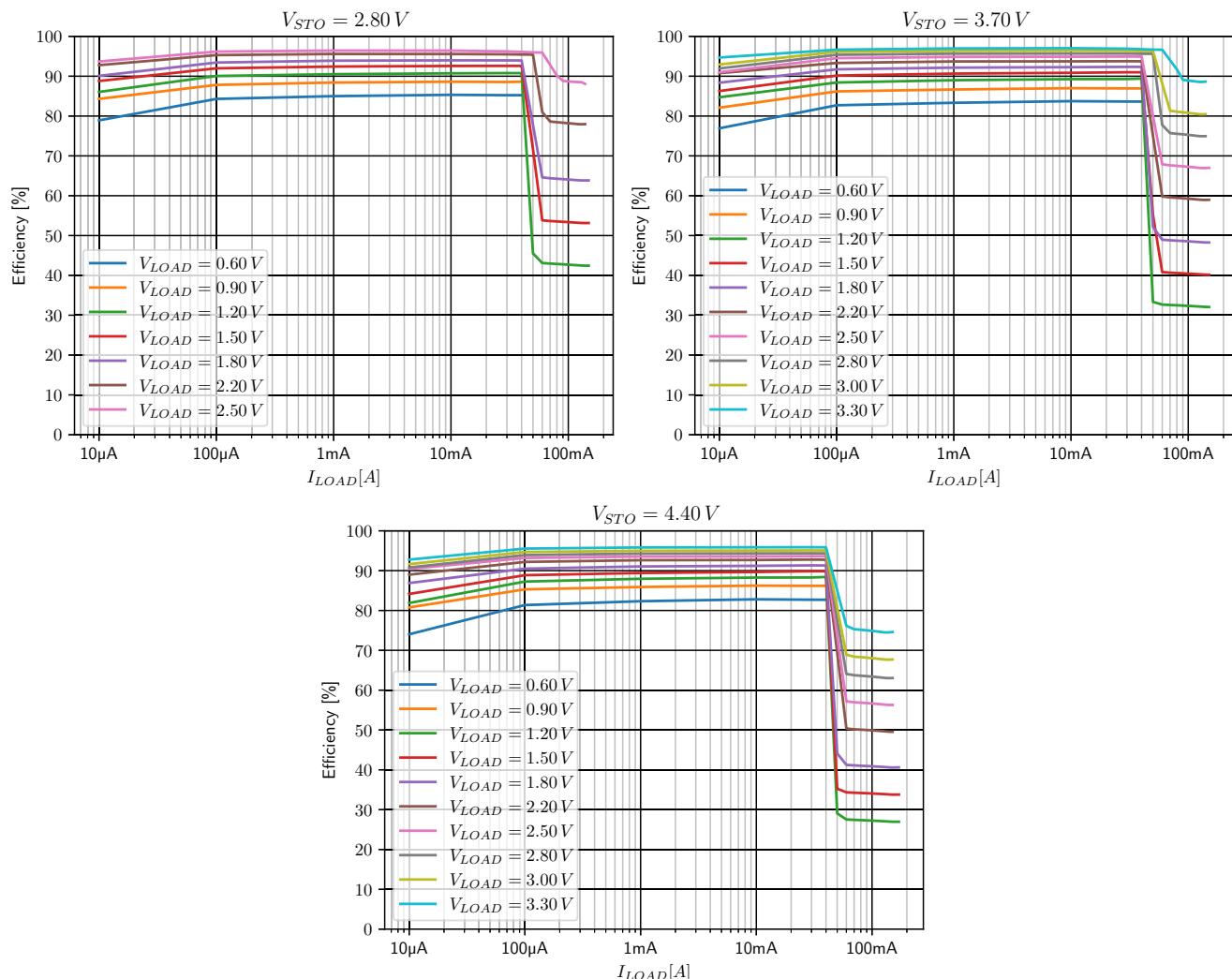

| Figure 3: SRCx to STO efficiency vs. $V_{SRCx}$ with $L_{BOOSTx} = 33 \mu\text{H}$ (Coilcraft LPS4018-333MRB),<br>BSTxCFG.TMULT = 0x02 (x3) ..... | 18 |

| Figure 4: STO to LOAD efficiency vs. $I_{LOAD}$ with $L_{BUCK} = 10 \mu\text{H}$ (TDK VLS252012CS-100M-1),<br>BUCKCFG.TMULT = 0x01 (x2) .....     | 19 |

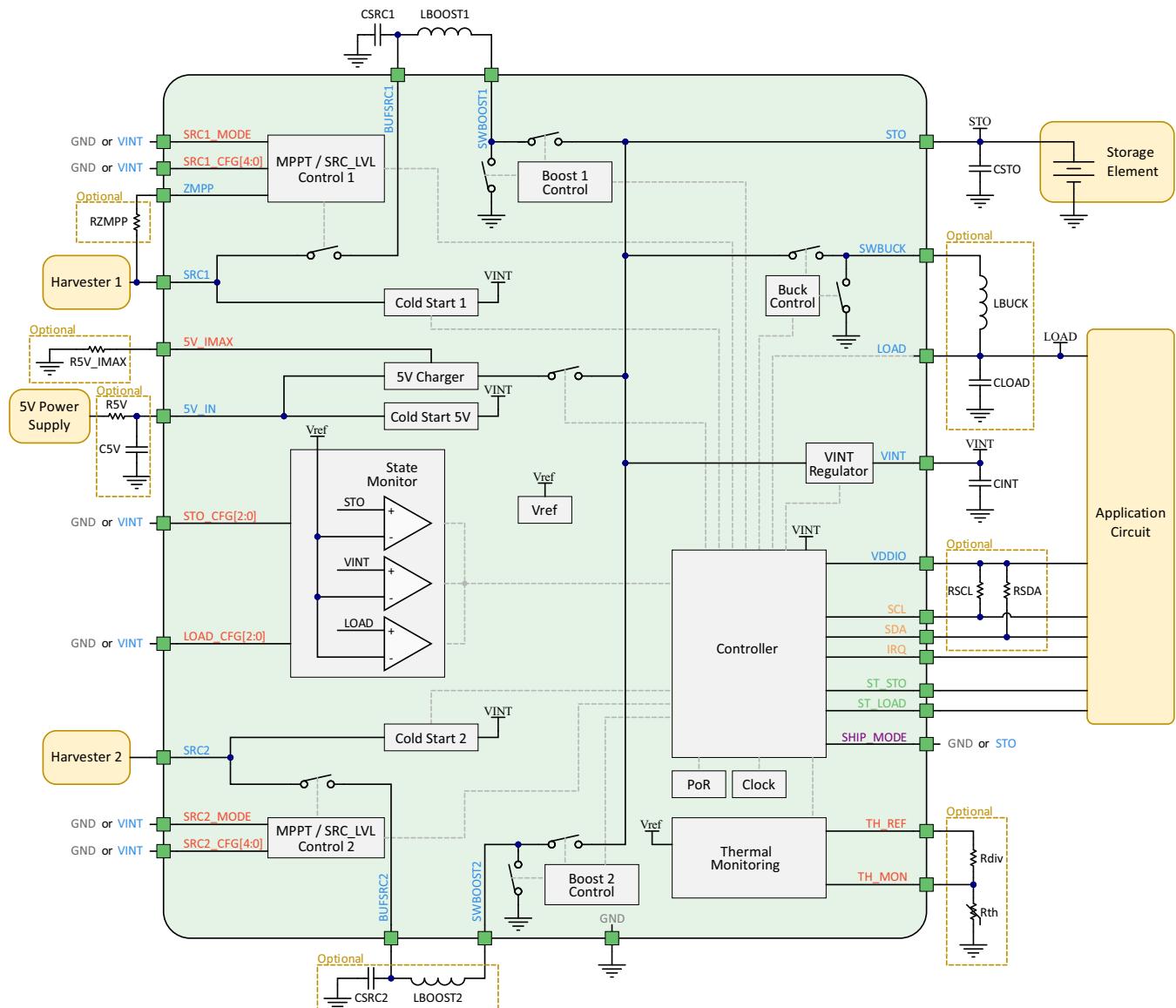

| Figure 5: Functional block diagram .....                                                                                                          | 20 |

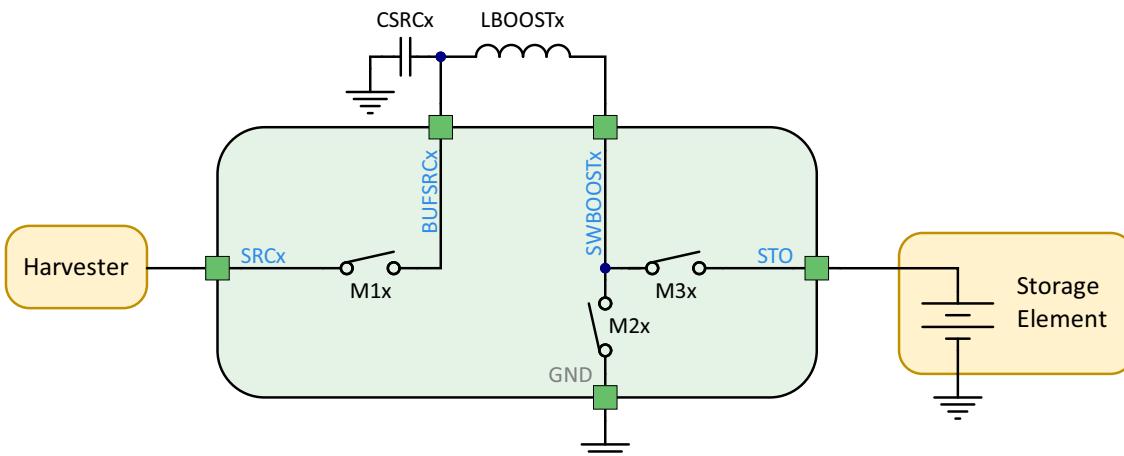

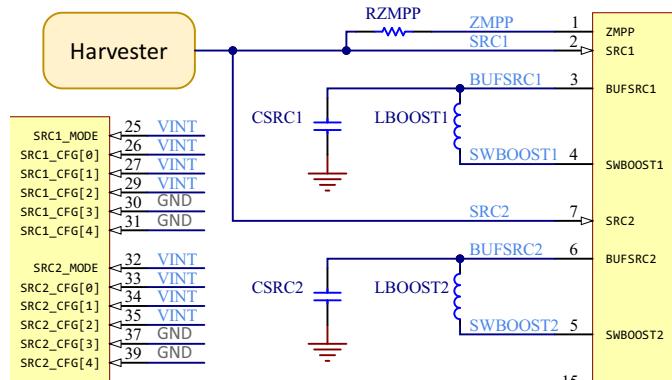

| Figure 6: Simplified schematic view of the boost converters .....                                                                                 | 21 |

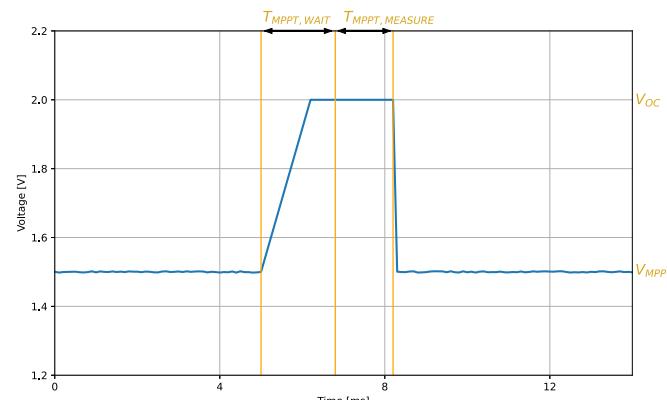

| Figure 7: MPPT evaluation behavior (with $T_{MPPT, WAIT}$ of 1.8 ms) .....                                                                        | 22 |

| Figure 8: ZMPP connection with both boost converters used in parallel .....                                                                       | 23 |

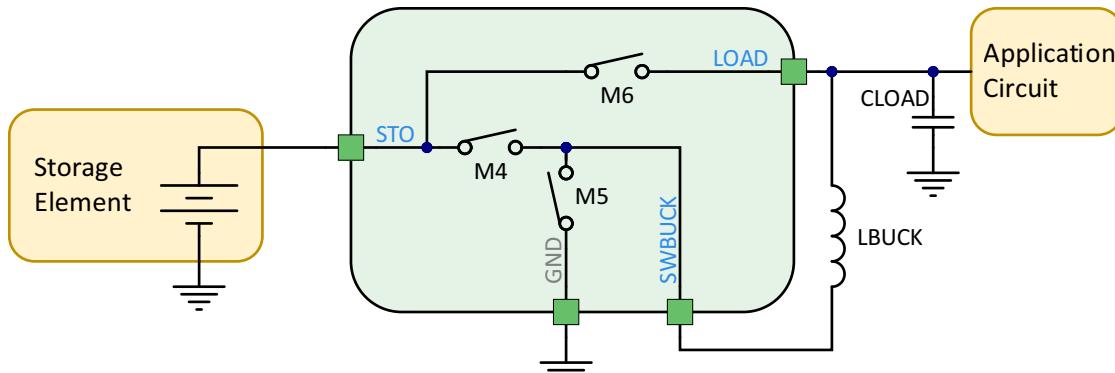

| Figure 9: Simplified schematic view of the buck converter .....                                                                                   | 24 |

| Figure 10: Average Power Monitoring in the power chain .....                                                                                      | 25 |

| Figure 11: State machine .....                                                                                                                    | 28 |

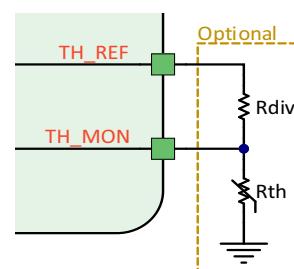

| Figure 12: TH_REF and TH_MON connections .....                                                                                                    | 36 |

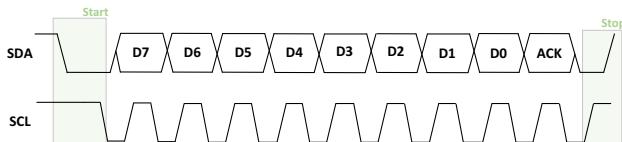

| Figure 13: I <sup>2</sup> C transmission frame .....                                                                                              | 38 |

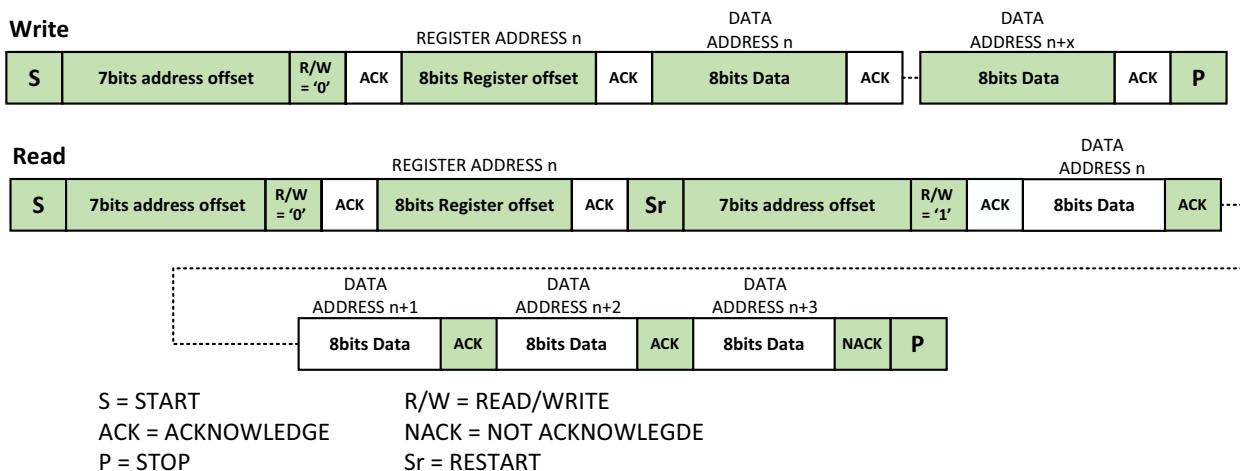

| Figure 14: Read and write transmission .....                                                                                                      | 39 |

| Figure 15: Typical application circuit 1 .....                                                                                                    | 76 |

| Figure 16: Typical application circuit 2 .....                                                                                                    | 78 |

| Figure 17: Typical application circuit 3 .....                                                                                                    | 80 |

| Figure 18: Schematic .....                                                                                                                        | 83 |

| Figure 19: Layout example .....                                                                                                                   | 85 |

| Figure 20: Tape and reel dimensions .....                                                                                                         | 86 |

| Figure 21: QFN 40-pin 5x5mm drawing (all dimensions in mm) .....                                                                                  | 87 |

| Figure 22: Recommended board layout for QFN40 package (all dimensions in mm) .....                                                                | 88 |

## List of Tables

|                                                                                                                          |    |

|--------------------------------------------------------------------------------------------------------------------------|----|

| Table 1: Pins description (part 1) .....                                                                                 | 10 |

| Table 2: Pins description (part 2) .....                                                                                 | 11 |

| Table 3: Pins description (part 3) .....                                                                                 | 12 |

| Table 4: Absolute maximum ratings .....                                                                                  | 13 |

| Table 5: ESD ratings .....                                                                                               | 13 |

| Table 6: Thermal data .....                                                                                              | 13 |

| Table 7: Electrical characteristics (part 1) .....                                                                       | 14 |

| Table 8: Electrical characteristics (part 2) .....                                                                       | 15 |

| Table 9: Electrical characteristics (part 3) .....                                                                       | 16 |

| Table 10: Recommended external components .....                                                                          | 17 |

| Table 11: Configuration of the source constant voltage regulation with SRCx_CFG[4:0] pins .....                          | 32 |

| Table 12: MPPT ratio configuration with SRCx_CFG[2:0] pins .....                                                         | 33 |

| Table 13: MPPT timing configuration with SRCx_CFG[4:3] pins .....                                                        | 33 |

| Table 14: Storage element thresholds configuration with STO_CFG[2:0] pins .....                                          | 34 |

| Table 15: Buck thresholds with STO_CFG[2:0] pins configuration depending on LOAD voltage .....                           | 34 |

| Table 16: Default temperature thresholds depending on STO_CFG[2:0] configuration with the recommended RDIV and RTH ..... | 35 |

| Table 17: Configuration of LOAD voltage with LOAD_CFG[2:0] .....                                                         | 36 |

| Table 18: Typical resistor values for setting 5 V charger max. current .....                                             | 37 |

| Table 19: Register map .....                                                                                             | 40 |

| Table 20: CTRL register .....                                                                                            | 43 |

| Table 21: VERSION register .....                                                                                         | 43 |

| Table 22: Summary of SRCxREGUx register fields .....                                                                     | 44 |

| Table 23: SRCxREGU0 register .....                                                                                       | 45 |

| Table 24: SRCxREGU1 register .....                                                                                       | 45 |

| Table 25: SRCx constant voltage values configured by SRCxREGUx (SRCxREGU0.MODE = 0) .....                                | 46 |

| Table 26: SRCx MPPT ratio/ZMPP configured by SRCxREGUx (SRCxREGU0.MODE = 1) .....                                        | 47 |

| Table 27: SRCx MPPT wait time configured by SRCxREGUx (SRCxREGU0.MODE = 1) .....                                         | 47 |

| Table 28: SRCx MPPT period configured by SRCxREGUx (SRCxREGU0.MODE = 1) .....                                            | 47 |

| Table 29: SRCLOW register .....                                                                                          | 48 |

| Table 30: $V_{SRCLOW}$ thresholds as configured by SRCLOW register .....                                                 | 48 |

| Table 31: VOVDIS register .....                                                                                          | 49 |

|                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------|----|

| Table 32: Storage element $V_{OVDIS}$ configuration by VOVDIS register .....                        | 49 |

| Table 33: VCHRDY register .....                                                                     | 50 |

| Table 34: Storage element $V_{CHRDY}$ configuration by VCHRDY register .....                        | 50 |

| Table 35: VCHRDYBUCK register .....                                                                 | 51 |

| Table 36: Storage element $V_{CHRDY,BUCK}$ configuration by VCHRDYBUCK register .....               | 51 |

| Table 37: VOVCH register .....                                                                      | 52 |

| Table 38: Storage element $V_{OVCH}$ configuration by VOVCH register .....                          | 52 |

| Table 39: BSTxCFG registers .....                                                                   | 53 |

| Table 40: Timing multiplier configured by TMULT field with corresponding boost inductor value ..... | 53 |

| Table 41: BUCKCFG register .....                                                                    | 54 |

| Table 42: Buck inductor values according to buck timing .....                                       | 54 |

| Table 43: $V_{LOAD}$ settings by BUCKCFG.VLOAD register .....                                       | 54 |

| Table 44: CHG5V register .....                                                                      | 55 |

| Table 45: $V_{5V,STOP}$ configuration by CHG5V register .....                                       | 55 |

| Table 46: TEMPcoldch register .....                                                                 | 56 |

| Table 47: TEMPphotch register .....                                                                 | 56 |

| Table 48: TEMPcolddis register .....                                                                | 57 |

| Table 49: TEMPphotdis register .....                                                                | 57 |

| Table 50: TEMpprotect register .....                                                                | 58 |

| Table 51: APM register .....                                                                        | 59 |

| Table 52: APMacc register .....                                                                     | 59 |

| Table 53: IRQENO register .....                                                                     | 60 |

| Table 54: IRQEN1 register .....                                                                     | 61 |

| Table 55: IRQflg0 register .....                                                                    | 62 |

| Table 56: IRQflg1 register .....                                                                    | 63 |

| Table 57: STATUS0 register .....                                                                    | 65 |

| Table 58: STATUS1 register .....                                                                    | 66 |

| Table 59: Summary of APMxSRCx and APMxLOAD register fields .....                                    | 67 |

| Table 60: Summary of APMxCHG5V register fields .....                                                | 68 |

| Table 61: APM0SRCx registers .....                                                                  | 69 |

| Table 62: APM1SRCx registers .....                                                                  | 69 |

| Table 63: APM2SRCx registers .....                                                                  | 69 |

| Table 64: APM0LOAD register .....                                                                   | 70 |

---

|                                                                                                      |    |

|------------------------------------------------------------------------------------------------------|----|

| Table 65: APM1LOAD register .....                                                                    | 70 |

| Table 66: APM2LOAD register .....                                                                    | 70 |

| Table 67: APM0CHG5V register .....                                                                   | 71 |

| Table 68: APM1CHG5V register .....                                                                   | 71 |

| Table 69: APMERR register .....                                                                      | 72 |

| Table 70: TEMP register .....                                                                        | 73 |

| Table 71: STO register .....                                                                         | 73 |

| Table 72: SRCx register .....                                                                        | 74 |

| Table 73: Source voltage $V_{SRCx}$ from SRCx.DATA register value (formula) .....                    | 74 |

| Table 74: Source voltage $V_{SRCx}$ from SRCx.DATA register value (lookup table) .....               | 74 |

| Table 75: PNO register .....                                                                         | 75 |

| Table 76: PN1 register .....                                                                         | 75 |

| Table 77: PN2 register .....                                                                         | 75 |

| Table 78: PN3 register .....                                                                         | 75 |

| Table 79: PN4 register .....                                                                         | 75 |

| Table 80: Summary of I <sup>2</sup> C register configuration for typical application circuit 3 ..... | 82 |

| Table 81: Minimum BOM .....                                                                          | 83 |

| Table 82: Moisture sensitivity level .....                                                           | 86 |

| Table 83: Revision history .....                                                                     | 92 |

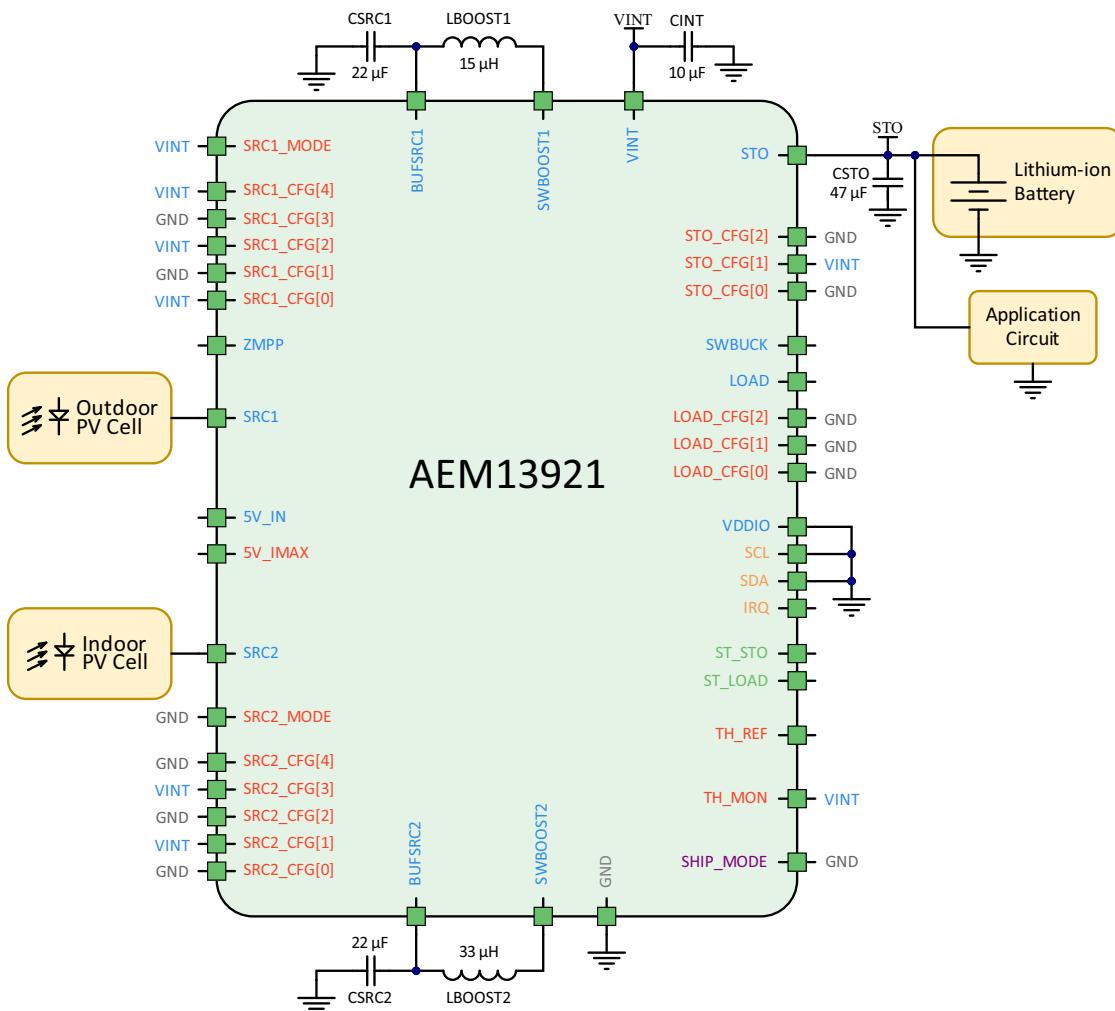

Figure 1: Simplified schematic view

## 1. Introduction

The AEM13921 is a full-featured energy efficient power management circuit able to harvest energy from two energy sources (connected to **SRC1** and/or **SRC2**) to charge a storage element (connected to **STO**) and to supply an application circuit (connected to **LOAD**). The storage element can also be charged from a 5 V power supply. This is done with a minimal bill of material.

The heart of the AEM13921 is composed of two switching boost converters for energy harvesting and a buck converter for supplying the load. All three have high power conversion efficiency.

The AEM13921 can be configured either by configuration pins or by a set of registers accessed through an I<sup>2</sup>C bus. Furthermore, some advanced configurations are accessible only through the I<sup>2</sup>C registers.

A 5 V power input **5V\_IN** allows for charging the storage element. This is done using a CC/CV (constant current / constant voltage) method. The CC mode maximum current can be configured between 13.5 mA and 135 mA with an external resistor. The CV mode can be enabled by I<sup>2</sup>C with a configurable charge stop voltage (**V<sub>5V,STOP</sub>**).

At first start-up, as soon as a required cold-start voltage of 275 mV and a sparse amount of power of at least 1.5  $\mu$ W is available on **SRCx** (**SRC1** or **SRC2**), the AEM13921 coldstarts. After the cold start, the AEM13921 extracts the power available from the sources if the working input voltage is above **V<sub>SRCx,REG</sub>** (constant voltage mode) or **V<sub>MPP</sub>** (MPPT mode). Cold start can also be done from the 5 V power supply input **5V\_IN**.

The storage element protection thresholds are configured through three configuration pins (**STO\_CFG[2:0]**), from which the user can select a specific operating mode out of 8 modes that cover most application requirements without any dedicated external component. If none of those 8 modes fits the user's storage element, the protection thresholds can also be configured individually through I<sup>2</sup>C registers to allow the user to define a mode with custom specifications.

The **ST\_STO** status pin provides information about the voltage level of the storage element, and the **ST\_LOAD** status pin about its readiness to supply an application through the AEM13921 **LOAD** output.

Both **SRCx** inputs of the AEM13921 can work in Maximum Power Point tracking (MPPT) mode or in constant voltage mode. The mode is configured with a dedicated pin **SRCx\_MODE** or through the I<sup>2</sup>C registers.

When in MPPT mode, the Maximum Power Point tracking (MPPT) ratio can be set through three configuration pins (**SRCx\_CFG[2:0]**) to ensure an optimum biasing of the harvester and maximize power extraction. Depending on the harvester, it is possible to adapt the timings of the MPP evaluations with the two configuration pins (**SRCx\_CFG[4:3]**) that sets the periodicity and the duration of the MPP evaluations. The MPPT ratio and the MPPT timings can also be configured through the I<sup>2</sup>C registers.

When in constant voltage mode, the source regulation voltage **V<sub>SRCx,REG</sub>** can be configured thanks to five configuration pins (**SRCx\_CFG[4:0]**). The constant voltage can also be configured through I<sup>2</sup>C registers for higher resolution and extended range of values.

If the storage element is sufficiently charged, the buck converter provides a regulated output voltage on the **LOAD** pin, allowing an application circuit to be supplied. The regulated voltage can be set through the **LOAD\_CFG[2:0]** pins or through the I<sup>2</sup>C registers.

A shipping mode feature can be enabled through the **SHIP\_MODE** pin, disabling the boost converters, the buck converter as well as the 5 V input, thus, preventing any charge or discharge of the storage element.

## 2. Pin Configuration and Functions

Figure 2: Pinout diagram

| NAME              | PIN NUMBER | FUNCTION                                                                                                                                                                                                                                                                         |

|-------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Power Pins</b> |            |                                                                                                                                                                                                                                                                                  |

| SRC1              | 2          | Connection to the energy source harvested by the boost converter #1 and #2 respectively.<br>Connect to GND if not used (typically for single source use of AEM13921).                                                                                                            |

| SRC2              | 7          |                                                                                                                                                                                                                                                                                  |

| BUFSRC1           | 3          | Connection to an external capacitor buffering the boost converter #1 and #2 inputs respectively.<br>Connect to GND if not used (typically for single source use of AEM13921).                                                                                                    |

| BUFSRC2           | 6          |                                                                                                                                                                                                                                                                                  |

| SWBOOST1          | 4          | Switching node of the boost converter #1 and #2 respectively.<br>Leave floating if not used (typically for single source use of AEM13921).                                                                                                                                       |

| SWBOOST2          | 5          |                                                                                                                                                                                                                                                                                  |

| ZMPP              | 1          | Connection for $R_{ZMPP}$ (see Section 5.2.2.2).<br>Leave floating if not used.                                                                                                                                                                                                  |

| STO               | 13         | Connection to the energy storage element (rechargeable storage element).                                                                                                                                                                                                         |

| SWBUCK            | 12         | Switching node of the buck converter.<br>If not used: <ul style="list-style-type: none"><li>- Disable buck converter through <b>LOAD_CFG[2:0]</b> pins or BUCKCFG.VLOAD register field.</li><li>- Leave the <b>SWBUCK</b> pin floating.</li></ul>                                |

| LOAD              | 14         | Output voltage of the buck converter to supply an application circuit.<br>If not used: <ul style="list-style-type: none"><li>- Disable buck converter through <b>LOAD_CFG[2:0]</b> pins or BUCKCFG.VLOAD register field.</li><li>- Leave the <b>LOAD</b> pin floating.</li></ul> |

| 5V_IN             | 15         | Input of the 5 V DC power supply.<br>Leave floating if not used.                                                                                                                                                                                                                 |

| VDDIO             | 17         | Voltage reference for the I <sup>2</sup> C interface, as well as for the <b>IRQ</b> pin. <ul style="list-style-type: none"><li>- If used, connect to a DC power supply.</li><li>- If not used, connect to GND.</li></ul>                                                         |

| VINT              | 28         | Connection for $C_{INT}$ buffering capacitor.<br>AEM13921 internal power supply (do not connect any external circuit on <b>VINT</b> ).                                                                                                                                           |

Table 1: Pins description (part 1)

| NAME                      | PIN NUMBER  | LOGIC LEVEL |      | FUNCTION                                                                                                                                                                     |                                                                                                                                                                              |

|---------------------------|-------------|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           |             | LOW         | HIGH |                                                                                                                                                                              |                                                                                                                                                                              |

| <b>Configuration Pins</b> |             |             |      |                                                                                                                                                                              |                                                                                                                                                                              |

| SRC1_MODE                 | 25          | GND         | VINT | Used to configure SRCx voltage regulation mode (see Section 5.2.1):<br>- LOW: constant voltage mode.<br>- HIGH: MPPT mode (ratio or ZMPP).<br>Read as HIGH if left floating. |                                                                                                                                                                              |

| SRC2_MODE                 | 32          | GND         | VINT |                                                                                                                                                                              |                                                                                                                                                                              |

| SRC1_CFG[4:0]             | SRC1_CFG[4] | 31          | GND  | VINT                                                                                                                                                                         | Used to configure SRCx regulation voltage.<br>SRCx_MODE = LOW (constant voltage mode, see Section 6.2):<br>- SRCx_CFG[4:0] are used to set SRCx constant regulation voltage. |

| SRC1_CFG[4:0]             | SRC1_CFG[3] | 30          | GND  | VINT                                                                                                                                                                         | SRCx_MODE = HIGH (MPPT ratio mode, see Section 6.3):<br>- SRCx_CFG[2:0] are used to set SRCx MPPT ratio.<br>- SRCx_CFG[4:3] are used to set SRCx MPPT timings.               |

| SRC1_CFG[4:0]             | SRC1_CFG[2] | 29          | GND  | VINT                                                                                                                                                                         |                                                                                                                                                                              |

| SRC1_CFG[4:0]             | SRC1_CFG[1] | 27          | GND  | VINT                                                                                                                                                                         |                                                                                                                                                                              |

| SRC1_CFG[4:0]             | SRC1_CFG[0] | 26          | GND  | VINT                                                                                                                                                                         |                                                                                                                                                                              |

| SRC2_CFG[4:0]             | SRC2_CFG[4] | 39          | GND  | VINT                                                                                                                                                                         |                                                                                                                                                                              |

| SRC2_CFG[4:0]             | SRC2_CFG[3] | 37          | GND  | VINT                                                                                                                                                                         |                                                                                                                                                                              |

| SRC2_CFG[4:0]             | SRC2_CFG[2] | 35          | GND  | VINT                                                                                                                                                                         |                                                                                                                                                                              |

| SRC2_CFG[4:0]             | SRC2_CFG[1] | 34          | GND  | VINT                                                                                                                                                                         |                                                                                                                                                                              |

| SRC2_CFG[4:0]             | SRC2_CFG[0] | 33          | GND  | VINT                                                                                                                                                                         |                                                                                                                                                                              |

| STO_CFG[2:0]              | STO_CFG[2]  | 24          | GND  | VINT                                                                                                                                                                         | Used to configure the storage element protection thresholds (see Section 6.4).<br>Read as HIGH if left floating.                                                             |

| STO_CFG[2:0]              | STO_CFG[1]  | 23          | GND  | VINT                                                                                                                                                                         |                                                                                                                                                                              |

| STO_CFG[2:0]              | STO_CFG[0]  | 22          | GND  | VINT                                                                                                                                                                         |                                                                                                                                                                              |

| LOAD_CFG[2:0]             | LOAD_CFG[2] | 11          | GND  | VINT                                                                                                                                                                         | Used to configure the LOAD output regulation voltage (see Section 6.6).<br>Read as HIGH if left floating.                                                                    |

| LOAD_CFG[2:0]             | LOAD_CFG[1] | 10          | GND  | VINT                                                                                                                                                                         |                                                                                                                                                                              |

| LOAD_CFG[2:0]             | LOAD_CFG[0] | 36          | GND  | VINT                                                                                                                                                                         |                                                                                                                                                                              |

| 5V_IMAX                   | 16          | Analog Pin  |      | Connection to an external resistor to set the charging current from the 5V_IN supply to STO (see Section 6.8).<br>Leave floating if the 5V_IN power supply is not used.      |                                                                                                                                                                              |

| TH_REF                    | 40          | Analog Pin  |      | Reference voltage for thermal monitoring (see Section 5.4).<br>Leave floating if not used.                                                                                   |                                                                                                                                                                              |

| TH_MON                    | 38          | Analog Pin  |      | Connection for the mid-point of the thermistor voltage divider (see Section 5.4).<br>Connect to VINT if not used.                                                            |                                                                                                                                                                              |

Table 2: Pins description (part 2)

| NAME                       | PIN NUMBER  | LOGIC LEVEL |       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|-------------|-------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            |             | LOW         | HIGH  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>Control Pin</b>         |             |             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SHIP_MODE                  | 8           | GND         | STO   | <p>Used to configure the shipping mode.</p> <p>When HIGH:</p> <ul style="list-style-type: none"> <li>- Minimum consumption from the storage element.</li> <li>- Storage element charge is disabled (Boost converters are disabled).</li> <li>- Buck (LOAD) is disabled.</li> <li>- VINT is only supplied from SRC1 and SRC2 if energy is available.</li> </ul> <p>Read as LOW if left floating.</p>                                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>I<sup>2</sup>C Pins</b> |             |             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SCL                        | 19          | GND         | VDDIO | <p>Unidirectional serial clock for I<sup>2</sup>C communication.</p> <p>Connect a pull-up resistor to VDDIO if used (see Section 6.1.2).</p> <p>Connect to GND if not used.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SDA                        | 20          | GND         | VDDIO | <p>Bidirectional data line for I<sup>2</sup>C communication.</p> <p>Connect a pull-up resistor to VDDIO if used (see Section 6.1.2).</p> <p>Connect to GND if not used.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IRQ                        | 18          | GND         | VDDIO | Logic output signal to indicate AEM13921 events to an external circuit GPIO.<br>Leave floating if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>Status Pin</b>          |             |             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ST_STO                     | 21          | GND         | STO   | <p>Logic output.</p> <ul style="list-style-type: none"> <li>- HIGH when in SUPPLY STATE or in SLEEP STATE.</li> <li>- LOW otherwise.</li> </ul> <p>Leave floating if not used.</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ST_LOAD                    | 9           | GND         | LOAD  | <p>Logic output, used when V<sub>LOAD</sub> is configured <math>\geq 1.2</math> V.</p> <ul style="list-style-type: none"> <li>- ST_LOAD is set HIGH if the buck converter is enabled, the temperature is within the range, and: <ul style="list-style-type: none"> <li>- V<sub>STO</sub> rises above V<sub>CHRDY,BUCK</sub> when the 5 V charger is not connected, or</li> <li>- V<sub>STO</sub> rises above V<sub>OVDIS,BUCK</sub> when the 5 V charger is connected.</li> </ul> </li> <li>- ST_LOAD is set LOW if: <ul style="list-style-type: none"> <li>- The buck converter is disabled, or</li> <li>- The temperature is outside the range, or</li> <li>- V<sub>STO</sub> remains below V<sub>OVDIS,BUCK</sub> for T<sub>CRIT,ST</sub>.</li> </ul> </li> </ul> <p>Leave floating if not used.</p> |

| <b>Other pins</b>          |             |             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| GND                        | Exposed Pad |             |       | Ground connection, must be strongly tied to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Table 3: Pins description (part 3)

### 3. Specifications

#### 3.1. Absolute Maximum Ratings

| Parameter                            |                                                                                                                                                            | Min  | Max  | Unit |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| Operating junction temperature $T_J$ |                                                                                                                                                            | -40  | 85   | °C   |

| Storage temperature $T_{stg}$        |                                                                                                                                                            | -65  | 150  | °C   |

| Input voltage                        | <code>SRCx, BUFSRCx, SWBOOSTx, ZMPP, STO, SWBUCK, 5V_IN, VDDIO, LOAD, SHIP_MODE, 5V_IMAX, LOAD_CFG[2], LOAD_CFG[1], SCL, SDA, IRQ, ST_STO, ST_LOAD.</code> | -0.3 | 5.50 | V    |

|                                      | <code>VINT, SRCx_MODE, SRCx_CFG[4:0], STO_CFG[2:0], LOAD_CFG[0], TH_REF, TH_MON.</code>                                                                    | -0.3 | 2.75 | V    |

Table 4: Absolute maximum ratings

#### 3.2. ESD Ratings

| Parameter                         |                                         | Value  | Unit |

|-----------------------------------|-----------------------------------------|--------|------|

| Electrostatic discharge $V_{ESD}$ | Human-Body Model (HBM) <sup>1</sup>     | ± 2000 | V    |

|                                   | Charged-Device Model (CDM) <sup>2</sup> | ± 1000 | V    |

Table 5: ESD ratings

1. ESD Human-Body Model (HBM) value tested according to JEDEC standard JS-001-2024.

2. ESD Charged-Device Model (CDM) value tested according to JEDEC standard JS-002-2022.

| ESD CAUTION                                                                         |                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | ESD (ELECTROSTATIC DISCHARGE) SENSITIVE DEVICE<br>These devices have limited built-in ESD protection and damage may thus occur on devices subjected to high-energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality |

#### 3.3. Thermal Resistance

| Package | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|---------|---------------|---------------|------|

| QFN-40  | 50            | 5             | °C/W |

Table 6: Thermal data

## 3.4. Electrical Characteristics at 25 °C

| Symbol                  | Parameter                                                                                                 | Conditions                                                   | Min                                       | Typ  | Max                                  | Unit |

|-------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------|------|--------------------------------------|------|

| <b>Power conversion</b> |                                                                                                           |                                                              |                                           |      |                                      |      |

| $P_{SRCx,CS}$           | Minimum source power required for cold start.                                                             |                                                              | 1.5                                       |      |                                      | μW   |

| $V_{SRCx,CS}$           | Minimum source voltage required for cold start.                                                           |                                                              | 0.275                                     |      |                                      | V    |

| $V_{MPP}$               | Target regulation voltage on $SRCx$ when extracting power.                                                | $SRCx\_MODE$ = HIGH.                                         | 0.12                                      |      | $V_{STO}$ <sup>1</sup>               | V    |

| $V_{SRCx,REG}$          | Target regulation voltage of the source, depending on GPIO or I <sup>2</sup> C configuration.             | $SRCx\_MODE$ = LOW, configured by $SRCx\_CFG[4:0]$ .         | 0.25                                      |      | min (3.18, $V_{STO}$ ) <sup>2</sup>  | V    |

|                         |                                                                                                           | $SRCx\_MODE$ = LOW, configured by I <sup>2</sup> C register. | 0.120                                     |      | min (4.455, $V_{STO}$ ) <sup>2</sup> | V    |

| $V_{OC}$                | Open-circuit voltage of the source.                                                                       |                                                              | 0.00 <sup>3</sup>                         |      | 5                                    | V    |

| $V_{5V\_IN}$            | Voltage on the $5V\_IN$ pin to allow for charging the storage element.                                    |                                                              | max (3.60, $V_{STO}$ + 0.20) <sup>4</sup> |      | 5.50                                 | V    |

| $I_{5V,CC}$             | Maximum charging current of the 5 V charger ( $5V\_IN$ input). Configured by the $R_{5V\_IMAX}$ resistor. | In constant current (CC) mode when $V_{STO} > V_{OVDIS}$ .   | 13.50                                     |      | 135                                  | mA   |

| $I_{5V,OVDIS,CC}$       | Charging current of the 5 V charger ( $5V\_IN$ input) in overdischarge.                                   | In constant current (CC) mode when $V_{STO} < V_{OVDIS}$ .   |                                           | 6.75 |                                      | mA   |

| $V_{VDDIO}$             | Voltage on $VDDIO$ .                                                                                      |                                                              | 1.50                                      |      | 5.00                                 | V    |

Table 7: Electrical characteristics (part 1)

1.  $V_{MPP}$  may exceed  $V_{STO}$  without causing damage to the AEM13921. However, doing so will reduce the boost converters efficiency.

2. The maximum value of  $V_{SRCx,REG}$  is determined by the highest configurable  $V_{SRCx,REG}$  but it must never be higher than  $V_{STO}$  to ensure proper operation.

3. When the open-circuit voltage is below the source regulation voltage (MPPT or constant voltage), the AEM13921 does not extract power from the source. Voltages down to GND voltage does not damage the AEM13921 though.

4. The 5 V charger is considered connected when the voltage on  $5V\_IN$  is greater than or equal to 3.60 V and at least 200 mV higher than the voltage on  $STO$ . It can be actively charging or not.

| Symbol             | Parameter                                                                                                                                                                                                 | Conditions                                                                              | Min   | Typ  | Max    | Unit |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|------|--------|------|

| <b>Timing</b>      |                                                                                                                                                                                                           |                                                                                         |       |      |        |      |

| $T_{MPPT,WAIT}$    | Wait time before $V_{OC}$ measurement begins during MPP evaluation (see Section 5.2.2).                                                                                                                   | Configured by $SRCx\_CFG[4:3]$ .                                                        | 1.8   |      | 233    | ms   |

|                    |                                                                                                                                                                                                           | Configured by I <sup>2</sup> C.                                                         |       |      | 465    |      |

| $T_{MPPT,MEASURE}$ | Duration of $V_{OC}$ measurement during MPP evaluation.                                                                                                                                                   |                                                                                         |       | 1.36 |        | ms   |

| $T_{MPPT,PERIOD}$  | Time between two MPP evaluations (see Section 5.2.2).                                                                                                                                                     | Configured by $SRCx\_CFG[4:3]$ .                                                        | 0.116 |      | 14.895 | s    |

|                    |                                                                                                                                                                                                           | Configured by I <sup>2</sup> C.                                                         |       |      |        |      |

| $T_{CRIT,ST}$      | Delay for the AEM13921 to notify the application about an overdischarged storage element, a temperature out of discharge temperature range, and to schedule <b>LOAD</b> output disable (see Section 5.3). |                                                                                         |       | 1.86 |        | s    |

| $T_{CRIT}$         | Delay for the AEM13921 to go in <b>OVDIS STATE</b> and to disable the <b>LOAD</b> output (see Section 5.9).                                                                                               |                                                                                         |       | 2.56 |        | s    |

| $T_{GPIO,MON}$     | GPIO monitoring rate.                                                                                                                                                                                     |                                                                                         |       | 1.86 |        | s    |

| $T_{STO,MON}$      | Storage element voltage monitoring rate.                                                                                                                                                                  | When the buck converter is disabled and the 5 V charger is not connected <sup>1</sup> . |       | 116  |        | ms   |

|                    |                                                                                                                                                                                                           | When the buck converter is enabled or the 5 V charger is connected <sup>1</sup> .       |       | 15   |        | ms   |

| $T_{TEMP,MON}$     | Temperature monitoring rate.                                                                                                                                                                              |                                                                                         |       | 7.45 |        | s    |

| $T_{5V,RISE}$      | Minimum rise time from 0 V to 5 V on the <b>5V_IN</b> pin (see Section 6.8).                                                                                                                              |                                                                                         |       | 50   |        | μs   |

Table 8: Electrical characteristics (part 2)

1. The 5 V charger is considered connected when the voltage on **5V\_IN** is greater than or equal to 3.60 V and at least 200 mV higher than the voltage on **STO**. It can be actively charging or not.

| Symbol                                         | Parameter                                                                                                                                                                                                                                                                                    | Conditions                                              | Min               | Typ                                    | Max               | Unit |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------|----------------------------------------|-------------------|------|

| <b>Storage element</b>                         |                                                                                                                                                                                                                                                                                              |                                                         |                   |                                        |                   |      |

| $V_{STO}$                                      | Voltage on the storage element.                                                                                                                                                                                                                                                              |                                                         | 2.40 <sup>1</sup> |                                        | 4.59 <sup>2</sup> | V    |

| $V_{OVDIS}$                                    | Voltage below which the storage element is considered to be fully depleted, and must not be discharged any further (see Section 6.4).                                                                                                                                                        | Configured by $STO\_CFG[2:0]$ .                         | 2.51              |                                        | 3.51              | V    |

|                                                |                                                                                                                                                                                                                                                                                              | Configured by I <sup>2</sup> C. <sup>3</sup>            | 2.400             |                                        | 3.581             | V    |